Product Summary

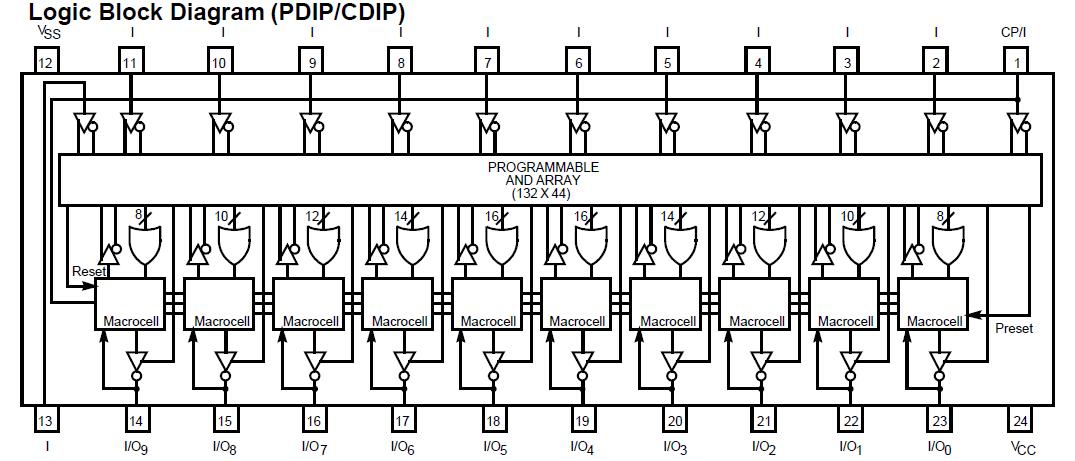

The Cypress PALCE22V10-15DMB is a CMOS Flash-erasable second-generation programmable array logic device. It is implemented with the familiar sum-of-products (AND-OR) logic structure and the programmable macrocell. The PALCE22V10-15DMB is executed in a 24-pin 300-mil molded DIP, a 300-mil cerDIP, a 28-lead square ceramic leadless chip carrier, a 28-lead square plastic leaded chip carrier, and provides up to 22 inputs and 10 outputs. The PALCE22V10-15DMB can be electrically erased and reprogrammed.

Parametrics

PALCE22V10-15DMB absolute maximum ratings: (1)Storage Temperature: –65℃ to +150℃; (2)Ambient Temperature with Power Applied: –55℃ to +125℃; (3)Supply Voltage to Ground Potential (Pin 24 to Pin 12): –0.5V to +7.0V; (4)DC Voltage Applied to Outputs in High-Z State: –0.5V to +7.0V; (5)DC Input Voltage: –0.5V to +7.0V; (5)Output Current into Outputs (LOW): 16 mA; (6)DC Programming Voltage: 12.5V; (7)Latch-up Current > 200 mA.

Features

PALCE22V10-15DMB features: (1)Low power: 90 mA max. commercial (10 ns), 130 mA max. commercial (5 ns); (2)CMOS Flash EPROM technology for electrical erasability and reprogrammability; (3)Variable product terms: 2x8 through 16) product terms; (4)User-programmable macrocell: Output polarity control, Individually selectable for registered or combinatorial operation; (5)Up to 22 input terms and 10 outputs; (6)DIP, LCC, and PLCC available:5 ns commercial version: 4 ns tCO, 3 ns tS, 5 ns tPD, 181-MHz state machine.

Diagrams

|

PALC16L8 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PALC16R4 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PALC16R6 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PALC16R8 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PALC22V10 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

PALC22V10-25PC |

|

IC SPLD 10MACROCELL 25NS 24-DIP |

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))